一、DC-DC變換器的基本工作原理

將使用最基本的類型來描述DC-DC變換器電路中升壓和降壓的工作原理。其他類型的電路或使用線圈的電路可以考慮由升壓電路和降壓電路或其應(yīng)用電路組合而成。

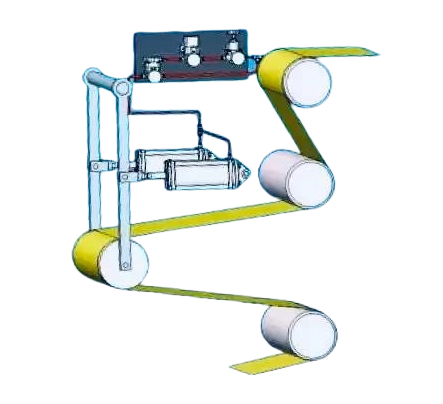

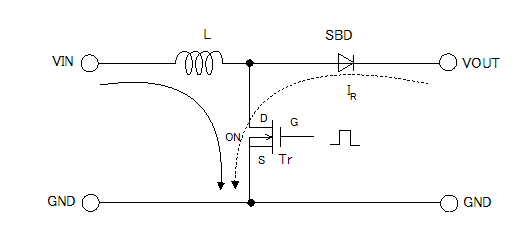

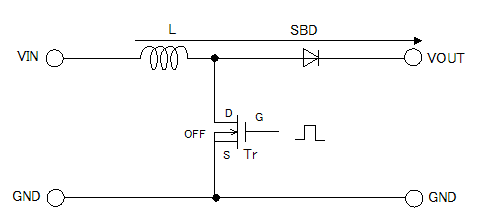

圖1和圖2說明了升壓電路的操作。圖1顯示了FET導(dǎo)通時的電流。虛線表示輕微的漏電流,這會降低輕負(fù)載時的效率。當(dāng)FET導(dǎo)通時,電能在L中累積。圖2顯示了FET關(guān)閉時的電流。當(dāng)場效應(yīng)管關(guān)斷時,L盡量保持上次電流值,將線圈左邊緣強行固定到V IN供電,使電壓升高到V OUT用于升壓操作。因此,如果FET的導(dǎo)通時間更長,則L中會積累更多的電流,從而可以獲取更大的功率。但是,如果FET導(dǎo)通時間過長,則向輸出側(cè)供電的時間太短,這段時間內(nèi)的損耗會增加,從而降低轉(zhuǎn)換效率。因此,通常確定最大占空比(開/關(guān)時間比)值以保持適當(dāng)?shù)闹怠?/p>

通過升壓操作,重復(fù)所示的電流流動:

升壓電路中FET導(dǎo)通時的電流

在升壓電路中關(guān)斷FET時的電流

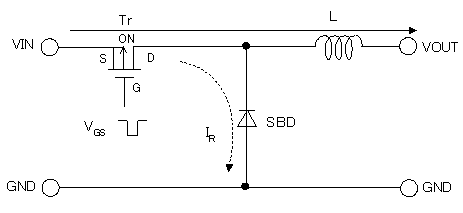

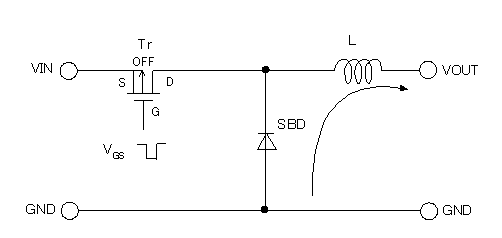

圖3和圖4說明了降壓電路的操作。圖3顯示了FET導(dǎo)通時的電流。虛線表示在輕負(fù)載條件下會降低效率的輕微漏電流。在FET導(dǎo)通期間,電能在L中累積并提供給輸出側(cè)。圖4顯示了FET關(guān)閉時的電流。當(dāng)FET關(guān)閉時,L嘗試保持最后的電流值并打開SBD。此時,線圈左邊緣的電壓被強行降到0V以下,降低了V OUT處的電壓.因此,如果FET的導(dǎo)通時間更長,則L中會積累更多的電流,從而可以獲取更大的功率。使用降壓電路,在FET導(dǎo)通時,可以向輸出側(cè)供電,不需要確定最大占空比。因此,如果輸入電壓低于輸出電壓,則FET保持導(dǎo)通。然而,由于升壓操作被禁用,輸出電壓也會降低到輸入電壓電平或更低。

通過降壓操作,重復(fù)所示的電流流動:

在降壓電路中打開FET時的電流

在降壓電路中關(guān)閉FET時的電流

二、設(shè)計DC-DC變換器電路的4個關(guān)鍵點:

在DC-DC變換器電路的規(guī)范要求中,以下被認(rèn)為是關(guān)鍵的:

1.運行穩(wěn)定(不會因開關(guān)異常、燒壞、過電壓等操作故障而崩潰)

2.高效率

3.輸出紋波小

4.良好的負(fù)載瞬態(tài)響應(yīng)

這些特性可以通過改變DC/DC變換器IC和外部部件在一定程度上得到改善。這四種屬性的權(quán)重因個別應(yīng)用而異。