集成電路是由不可分離的組件組成的電路,這些組件以防止IC因建筑或商業(yè)目的而分離的方式電耦合在一起。這種電路可以使用多種技術(shù)來構(gòu)建。單片集成電路現(xiàn)在被稱為ic。

1、集成電路設(shè)計(jì)技術(shù)。

需要快速設(shè)計(jì)大型、復(fù)雜的處理器,以利用摩爾定律賦予的大量晶體管。復(fù)雜性是讓巨大的芯片正常運(yùn)行的障礙;許多好的芯片創(chuàng)意被埋沒在細(xì)節(jié)的海洋中,在芯片工作之前必須解決這些細(xì)節(jié)。集成電路設(shè)計(jì)具有挑戰(zhàn)性,因?yàn)楣こ處煴仨毱胶飧鞣N問題:

2、不同程度的抽象

提煉IC的想法需要很多層的細(xì)節(jié)。設(shè)計(jì)師必須從芯片的功能規(guī)范開始,將功能擴(kuò)展為架構(gòu),然后將架構(gòu)擴(kuò)展為邏輯設(shè)計(jì),最后將邏輯設(shè)計(jì)擴(kuò)展為版圖。

3、多重且相互沖突的成本

設(shè)計(jì)師不僅必須通過多個(gè)細(xì)節(jié)層次勾勒出設(shè)計(jì)草圖,還必須考慮成本不是貨幣費(fèi)用,而是評(píng)估設(shè)計(jì)質(zhì)量的標(biāo)準(zhǔn)。芯片的運(yùn)行速度是一項(xiàng)關(guān)鍵成本。在執(zhí)行相同任務(wù)(例如乘法)時(shí),兩種架構(gòu)可以以截然不同的速率工作。將看到芯片面積是另一個(gè)關(guān)鍵的設(shè)計(jì)成本,因?yàn)楦緹o法制造大于1平方厘米的芯片,而制造芯片的成本與其面積成指數(shù)關(guān)系。此外,如果必須滿足多個(gè)成本標(biāo)準(zhǔn)(例如面積和速度要求),許多設(shè)計(jì)選擇將以犧牲另一個(gè)為代價(jià)來改進(jìn)一個(gè)成本統(tǒng)計(jì)數(shù)據(jù)。平衡對(duì)立限制的做法推動(dòng)了設(shè)計(jì)。

4、設(shè)計(jì)時(shí)間短

設(shè)計(jì)師將有時(shí)間考慮設(shè)計(jì)選擇如何影響完美世界中的最終產(chǎn)品。然而,生活的世界并不完美。如果芯片發(fā)布得太晚,它們的銷售額可能會(huì)因?yàn)楦偁帉?duì)手竊取市場(chǎng)份額而變得微不足道或根本不存在。因此,設(shè)計(jì)人員面臨盡快制造芯片的壓力。要將概念開發(fā)成功能性ASIC,在特定應(yīng)用IC設(shè)計(jì)的情況下可能只有幾周的時(shí)間。設(shè)計(jì)抽象和分層設(shè)計(jì)是設(shè)計(jì)師為消除無關(guān)細(xì)節(jié)而創(chuàng)建的兩種策略。設(shè)計(jì)人員還廣泛使用計(jì)算機(jī)輔助設(shè)計(jì)技術(shù)來評(píng)估和綜合設(shè)計(jì)。

5、分層設(shè)計(jì)

成分

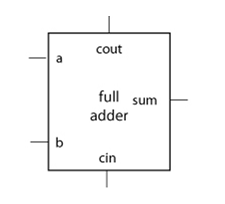

芯片設(shè)計(jì)人員可以通過將芯片分解為組件層次結(jié)構(gòu)來分而治之。如下圖所示,一個(gè)零件包括一個(gè)主體和幾個(gè)引腳;全加器包含引腳a、b、cin、cout和sum。如果以這個(gè)全加器為規(guī)范,可以創(chuàng)建許多這種類型的實(shí)例。重復(fù)經(jīng)常使用的部分通常很有幫助,例如,當(dāng)從n個(gè)全加器創(chuàng)建一個(gè)n位加法器時(shí)。

6、設(shè)計(jì)抽象

建模級(jí)別

設(shè)計(jì)抽象對(duì)于硬件系統(tǒng)的開發(fā)至關(guān)重要。為監(jiān)督設(shè)計(jì)過程并確保實(shí)現(xiàn)速度和功耗等關(guān)鍵設(shè)計(jì)目標(biāo),硬件設(shè)計(jì)人員采用了多種設(shè)計(jì)抽象層。邏輯門是設(shè)計(jì)抽象的最基本圖示。用于構(gòu)造門的非線性電路被簡化為邏輯門,它只接受二進(jìn)制布爾值。當(dāng)用邏輯門表示時(shí),一些設(shè)計(jì)工作(例如準(zhǔn)確的延遲計(jì)算)變得困難或不可能。其他設(shè)計(jì)活動(dòng),如邏輯優(yōu)化,太費(fèi)力而無法在電路上進(jìn)行。選擇最適合設(shè)計(jì)任務(wù)的設(shè)計(jì)抽象。

更高的抽象也可用于使用更精確的模型來改進(jìn)初始決策。例如,經(jīng)常使用直接的延遲計(jì)算來優(yōu)化邏輯,然后再使用精確的電路數(shù)據(jù)改進(jìn)邏輯設(shè)計(jì)。層次結(jié)構(gòu)和設(shè)計(jì)抽象是不一樣的。例如,由布爾邏輯函數(shù)構(gòu)成的架構(gòu)使用與設(shè)計(jì)層次結(jié)構(gòu)中使用的組件具有相同抽象程度的組件。訂單的每個(gè)級(jí)別都通過引入更多組件來增加復(fù)雜性。由于它被重鑄為較低的抽象級(jí)別,因此組件的數(shù)量可能不會(huì)改變;這些組件的更復(fù)雜行為增加了復(fù)雜性。

7、自上而下和自下而上的設(shè)計(jì)

設(shè)計(jì)總是需要從最不抽象的描述開始,從抽象層次的頂部開始下降。向抽象中添加有用的信息必須是設(shè)計(jì)過程的第一步。然而,自上而下的設(shè)計(jì)選擇是在對(duì)每個(gè)抽象級(jí)別可用的備選方案知之甚少的情況下做出的。希望選擇最能滿足的速度、面積和功率需求的候選者。

在進(jìn)行早期設(shè)計(jì)之前,無法準(zhǔn)確估算此類費(fèi)用。自下而上的分析和設(shè)計(jì)將成本信息傳播到更高的抽象層次;例如,可能會(huì)使用來自電路設(shè)計(jì)的更精確的延遲信息來重新設(shè)計(jì)邏輯。在完成實(shí)施之前,經(jīng)驗(yàn)將幫助估算費(fèi)用,但大多數(shù)設(shè)計(jì)都需要自上而下的設(shè)計(jì)循環(huán),然后是自下而上的重新設(shè)計(jì)。